# **CRAY Y-MP<sup>\*</sup> Computer Systems Functional Description Manual**

HR-04001-0C

Cray Research, Inc.

Copyright © 1990 Cray Research, Inc. Portions of the Autotasking documentation Copyright © 1988 Pacific-Sierra Research Corporation. This manual or parts thereof may not be reproduced in any form unless permitted by contract or by written permission of Cray Research, Inc.

The CRAY Y-MP computer system is exempt from the technical requirements of the FCC's Part 15 Subpart J rules pursuant to Section 15.801 (C).

CRAY®, CRAY-1®, CRAY Y-MP®, HSX®, SSD®, and UNICOS® are federally registered trademarks and Autotasking<sup>™</sup>, CFT<sup>™</sup>, CFT77<sup>™</sup>, CFT2<sup>™</sup>, CRAY X-MP<sup>™</sup>, COS<sup>™</sup>, Cray Ada<sup>™</sup>, CRAY-2<sup>™</sup>, CRAY Y-MP2E<sup>™</sup>, CSIM<sup>™</sup>, Delivering the power . . .<sup>™</sup>, IOS<sup>™</sup>, OLNET<sup>™</sup>, RQS<sup>™</sup>, SEGLDR<sup>™</sup>, SUPERLINK<sup>™</sup>, and X-MP EA<sup>™</sup> are trademarks of Cray Research, Inc.

Amdahl is a registered trademark of Amdahl Corporation. AOS is a registered trademark of Data General Corporation. Apollo and DOMAIN are registered trademarks of Apollo Computer Inc. CDC is a registered trademark of Control Data Corporation. ECLIPSE is a registered trademark of Data General Corporation. Ethernet is a registered trademark of the Xerox Corporation. Fluorinert liquid is a registered trademark of 3M. HYPERbus and HYPERchannel are registered trademarks of Network Systems Corporation. IBM is a registered trademark of International Business Machines Corporation. UNISYS is a registered trademark of UNISYS Corporation. UNIX is a registered trademark of AT&T.

AEGIS is a trademark of Apollo Computer Inc. CYBER is a trademark of Control Data Corporation. DEC, PDP, VAX, VAXcluster, and VMS are trademarks of Digital Equipment Corporation. Honeywell is a trademark of Honeywell, Incorporated. LANIord is a trademark of Computer Network Technology. Sun-3 is a trademark of Sun Microsystems, Inc. VMEbus is a trademark of Motorola, Inc. The UNICOS operating system is derived from the AT&T UNIX System V operating system. UNICOS is also based in part on the Fourth Berkeley Software Distribution under license from The Regents of the University of California.

MVS, VM, and VM/CMS are products of International Business Machines Corporation. NOS, NOS/BE, and NOS/VE are products of Control Data Corporation.

Requests for copies of Cray Research, Inc. publications should be directed to:

CRAY RESEARCH, INC. Distribution 2360 Pilot Knob Road Mendota Heights, MN 55120 (800) 284-2729 extension 5907

Comments about this publication should be directed to:

CRAY RESEARCH, INC. Hardware Publications and Training 770 Industrial Blvd. Chippewa Falls, WI 54729

### Title: CRAY Y-MP Computer Systems Functional Description Manual

Number: HR-04001-0C

Your feedback on this publication will help us provide better documentation in the future. Please take a moment to answer the few questions below.

For what purpose did you primarily use this manual?

\_\_\_\_\_Troubleshooting

\_\_\_\_\_Tutorial or introduction

\_\_\_\_\_Reference information

\_\_\_\_Classroom use

\_\_\_\_Other - please explain

Using a scale from 1 (poor) to 10 (excellent), please rate this manual on the following criteria and explain your ratings:

| Accuracy                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Organization                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Readability                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Physical qualities (binding, pri | nting, page layout)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Amount of diagrams and photos    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Quality of diagrams and photos   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Completeness (Check one)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Too much information             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Too little information           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T                                | <ul> <li>Commission and the statements of the statement of the stateme</li></ul> |

\_\_\_\_\_Just the right amount of information

Your comments help Hardware Publications and Training improve the quality and usefulness of your publications. Please use the space provided below to share your comments with us. When possible, please give specific page and paragraph references. We will respond to your comments in writing within 48 hours.

| NAME      |                                       |     | in a chuir an ann an |

|-----------|---------------------------------------|-----|----------------------------------------------------|

| JOB TITLE |                                       |     | <u>-</u> 2                                         |

| FIRM      |                                       |     |                                                    |

| ADDRESS   |                                       |     | RESEARCH, INC.                                     |

| CITY      | STATE                                 | ZIP | -                                                  |

| DATE      | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |     |                                                    |

|           |                                       |     |                                                    |

[or attach your business card]

Fold

Fold

# **Record of Revision**

Each time this manual is revised and reprinted, all changes issued against the previous version are incorporated into the new version and the new version is assigned a new alphabetic level.

Every page of a manual changed by a reprint with revision has the revision level indicated in the publication number in the ninth position. Changes to part of a page are indicated by a change bar in the margin directly opposite the change. A change bar in the footer indicates that most, if not all, of the page is new. If the manual is rewritten, the revision level changes but the manual does not contain change bars.

| REVISION | DESCRIPTION                                                                                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | January 1988 - Original printing.                                                                                                                                                                                                                                              |

| А        | February 1989 - This revision adds information about new products: the CRAY Y-MP8, CRAY Y-MP4, and CRAY Y-MP2 models, and the DS-40D Disk Subsystem. This revision also incorporates readers' comments.                                                                        |

| В        | September 1989 - This revision adds register parity information for the CRAY Y-MP computer system. Change bars have been added to indicate where this register parity information was incorporated. Various technical and editorial changes have also been made.               |

| B1       | January 1990 - This change packet includes information on the new CRAY Y-MP<br>128-Mword central memory. All of the CRAY Y-MP specification sheets were<br>updated and a new specification sheet for the FOL-3 fiber-optic link was added. The<br>following changes were made: |

|          | • On page vii, the following related publication was added: <i>Principles of Computer Room Design</i> , publication number HR-04013.                                                                                                                                           |

|          | • On page 1-6, the statement, "The MWS is not connected to the customer's network." was added.                                                                                                                                                                                 |

|          | • On page 2-6, the corrected statement now reads, "Each CPU now contains 8 registers."                                                                                                                                                                                         |

|          | • On page 2-37: "A 2-parcel or 3-parcel instruction begins in any parcel of a word and can span a word boundary."                                                                                                                                                              |

|          | Change bars are included for your convenience.                                                                                                                                                                                                                                 |

| С        | June 1990. This revision incorporates change packet $HR-04001-0B1$ and adds information on the new DS-41 Disk Subsystem.                                                                                                                                                       |

|          |                                                                                                                                                                                                                                                                                |

### 영광하다 말한 수밖을 걸었는데, 나라 다

ako barra di komuna di kumunika dan anta kunikan ngga sikan barra da parama na ala ata angganikala na munun na Anta ang barra dan sikan kana da barra da para da si

יוראי בקשע אבר שנה הראש שישול היים שנה היידא ליישיים שנה היינעשים היים האינה אלים היידה עלה היידי יידקה שביה ש עלשראה לשבריים או היידא יישולה להקריה ביל הנשיקים בישיים שנה היידה איז היידה היידה השנה היל שבניה אם עלה לעשייה הלשויים שבניה הלשבעיה

المعمد من الكريمة المعارضة من يعتقد من المعارضة الم المعارضة الم

ו "אוקעל באיר אויד ללאול אי "להגאוריי" – אינאים שלולה ציע א' יידיייי האורילא לבעור אינה לאיר עלאים לבעול לי "אילע א איזייייי האסטרי אינאיע יון העליבציי אוי לדייי לבאורי בניין הייביים אוני אוילא בערילים לא האלאים איני לבעול לי "א "לא אוג אלא באיר לאינה" "לא אוג אלא לאילא - יי

표는 한 가지만 한 것 같은 모두 가슴 가슴 가지 않는다. 이 가지 않으며 이 가지만 것 같은 것 같 같은 것 - 신고는 고려만한 하고도 관한 것 같은 안정합성과 같은 것 이라는 것 같 같은 것 같은 것

ा सम्पर्क हिन्दी ही सम्प्रेस सम्प्रदान के दिन हो। से दिन से स्थान संप्रेल से सम्पर्क से स्थान हो। स्थान के स्थि सहस्य सम्प्रदुष्ट्री से सम्प्रही हो आ

가는 정도를 가셨는 것 않는 것이 가지 않는 것이라. 또는 가지 않는 것이 가지 않는 것이 가지 않아? 이 것도 같이 다 있었다. 같이 있는 것이 같이 있다. 1941년 - 대부분이 이 아이 1951년 - 대부분이 이 아이

요즘 사람은 적용 방법을 다 있다. 이 것은 방법을 위한 이 가지 않는 것을 가 많을까?

- 4.1.11 전 1997 - 10 2017 관소가 가지 아파가 4.1 2017 - 2017 - 2017 - 2017 전 1997 - 2017 전 1997 - 2017 전 1997 \* 2017 - 2017 전 2017 - 2017 - 2017 - 2017 전 1997 - 2017 - 2017 - 2017

## PREFACE

This manual describes the basic functions of the CRAY Y-MP computer system currently manufactured by Cray Research, Inc.

### AUDIENCE

This manual is written primarily for customers. It describes the design and architecture of the CRAY Y-MP computer system and its associated peripheral devices.

## ORGANIZATION

This manual is organized into the following tabbed sections. A detailed Table of Contents is included at the beginning of each tabbed section.

SECTION 1 - CRAY Y-MP COMPUTER SYSTEM OVERVIEW introduces and describes the CRAY Y-MP system components and support equipment.

SECTION 2 - CRAY Y-MP MAINFRAME describes the basic architecture of the CRAY Y-MP mainframe. This section is divided into two subsections. The first subsection describes the hardware architecture of the mainframe. The second subsection describes the CPU instructions. Three specification sheets (one each for the CRAY Y-MP8, CRAY Y-MP4, and CRAY Y-MP2 computer systems) are included at the end of this section

SECTION 3 - I/O SUBSYSTEM describes the basic architecture and functions of the I/O Subsystem (IOS). A specification sheet for the IOS is included at the end of this section.

SECTION 4 - SSD SOLID-STATE STORAGE DEVICE describes the basic architecture and functions of the SSD solid-state storage device. A specification sheet for the SSD is included at the end of this section.

SECTION 5 - PERIPHERAL EQUIPMENT describes the function of the disk drives and network interface equipment used by the CRAY Y-MP computer system. Specification sheets for the the different disk drives and network interfaces are included at the end of this section

SECTION 6 SOFTWARE OVERVIEW provides an overview of the software available for the CRAY Y-MP computer system.

For the reader's convenience, a glossary is included. It defines many of the commonly used abbreviations and terminology associated with the CRAY Y-MP computer system.

## NOTATIONAL CONVENTIONS

The following conventions are used throughout this manual.

| Description                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Variable information.                                                                                                                                                                                                                                                                                                                                       |

| An unused value.                                                                                                                                                                                                                                                                                                                                            |

| A specified value.                                                                                                                                                                                                                                                                                                                                          |

| The <b>contents</b> of the register or memory location designated by value.                                                                                                                                                                                                                                                                                 |

| Register bits are numbered from right to left as powers of 2.<br>Bit $2^0$ corresponds to the least significant bit of the register.<br>One exception is the Vector Mask register. The Vector<br>Mask register bits correspond to a word element in a vector<br>register; bit $2^{63}$ corresponds to element 0 and bit $2^0$<br>corresponds to element 63. |

| All numbers used in this manual are decimal, unless<br>otherwise indicated. Octal numbers are indicated with an 8<br>subscript. Exceptions are register numbers, the instruction<br>parcel in instruction buffers, and instruction forms, which                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                             |

The following are examples of the preceding conventions.

| Example                     | Description                                                                                                      |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|

| Transmit $(Ak)$ to $Si$     | Transmit the contents of the A register specified by the $k$ field to the S register specified by the $i$ field. |

| 167 <i>ixk</i>              | Machine instruction 167. The $j$ field is not used.                                                              |

| Read n words from<br>memory | Read a specified number of words from memory.                                                                    |

| Bit 2 <sup>63</sup>         | The value represents the most significant bit of an S register or element of a V register.                       |

| 10008                       | The number base is octal.                                                                                        |

|                             |                                                                                                                  |

## **RELATED PUBLICATIONS**

For additional information on site planning, refer to the following publications.

- HR-00080 The Cray Peripheral Equipment Site Planning Reference Manual provides site planning information for operator and maintenance workstation equipment, Disk Storage units (DSUs), and Front-end Interface (FEI) cabinets.

- HR-00082 The Cray Support Equipment Site Planning Reference Manual provides site planning information for Refrigeration Condensing units (RCUs) and Motor-generator sets (MGSs).

- HR-00306 The Safe Use and Handling of Fluorinert Liquids is written for Cray Research, Inc. customers and field engineers whose Cray computer system uses Fluorinert liquid, warns and informs about using Fluorinert liquid, and describes its uses at Cray Research, Inc. The manual describes the Material Safety Data Sheet and explains its significance in using Fluorinert liquid or any other chemical.

- HR-04000 The CRAY Y-MP8 Computer Systems Site Planning Reference Manual provides site planning information for the CRAY Y-MP mainframe, the mainframe Heat Exchanger Unit (HEU), the I/O Subsystem (IOS), the SSD Solid-state Storage Device, and the IOS and SSD Power Distribution Units (PDUs).

- HR-04002 The CRAY Y-MP2 Computer Systems Site Planning Reference Manual provides site planning information for the CRAY Y-MP2 computer system. It contains technical information to plan and prepare a typical site for installing a CRAY Y-MP2 computer system.

- HR-04003 The CRAY Y-MP4 Computer Systems Site Planning Reference Manual provides site planning information for the CRAY Y-MP4 computer system. It contains technical information to plan and prepare a typical site for installing a CRAY Y-MP4 computer system.

- HR-04013 The *Principles of Computer Room Design* manual describes computer room design principles to help computer room facility managers prepare, inspect, and maintain a stable, problem-free environment. Computer room and raised-floor construction, system cooling, environmental control, fire and lightning protection, power, and grounding are also discussed.

- SN-03030 The Operator Workstation (OWS) Guide describes the commands and operation of the VME-based OWS used for CRAY Y-MP and CRAY X-MP EA computer system operation and monitoring. This manual is for computer operators and system administrators.

• SR-00085 The Symbolic Machine Instructions Reference Manual describes the machine instructions used on CRAY-1, CRAY X-MP, and CRAY Y-MP computer systems.

A list of related software publications is included at the end of Section 6, "Software Overview."

Please use one of the reader comment forms located at the front and back of this manual to suggest improvements or point out technical errors.

viii

# CONTENTS

| 1 - C  | RAY Y-MP COMPUTER SYSTEM OVERVIEW                  | 1-1  |

|--------|----------------------------------------------------|------|

|        | CRAY Y-MP Mainframe                                | 1-3  |

|        | I/O Subsystem                                      | 1-3  |

|        | SSD Solid-state Storage Device                     | 1-4  |

|        | Disk Storage Units                                 | 1-5  |

|        | Network Interfaces                                 | 1-5  |

|        | Operator and Maintenance Workstations              | 1-6  |

|        | Power and Cooling Support Equipment                | 1-6  |

|        |                                                    | 1-0  |

| 2 - C  | RAY Y-MP MAINFRAME                                 | 2-1  |

|        | CPU Shared Resources                               | 2-1  |

|        | CPU Computation Section                            |      |

|        |                                                    | 2-22 |

|        | Special Features of the CRAY Y-MP Computer System  | 2-22 |

|        |                                                    | 2-25 |

|        |                                                    |      |

|        |                                                    | 2-67 |

|        |                                                    | 2-71 |

|        | CRAY Y-MP2 Computer System Specification Sheet     | 2-75 |

| 3 - I/ | O SUBSYSTEM                                        | 3-1  |

| 0 1/   | I/O Processors                                     |      |

|        | I/O Subsystem Buffer Memory                        | 3-1  |

|        |                                                    | 3-4  |

|        | System Operator Workstation                        | 3-4  |

|        | I/O Subsystem Model D Specification Sheet          | 3-5  |

| 1.5    | SD SOLID-STATE STORAGE DEVICE                      | 4.1  |

| 4-01   |                                                    | 4-1  |

|        |                                                    | 4-1  |

|        | SSD Memory Size                                    | 4-2  |

|        | SSD Memory Transfer and Data Protection            | 4-2  |

|        | SSD Solid-state Storage Device Specification Sheet | 4-3  |

| 5.P    | ERIPHERAL EQUIPMENT                                | F 1  |

| 0      |                                                    | 5-1  |

|        | Disk Controller Units and Disk Storage Units       | 5-1  |

|        | Disk Controller Units                              | 5-1  |

|        | Disk Storage Units                                 | 5-1  |

|        | DS-40 Disk Subsystem                               | 5-2  |

|        | DS-40 Disk Subsystem Standard Configurations       | 5-3  |

|        | DS-40D Disk Daisy Chain Configurations             | 5-3  |

## PERIPHERAL EQUIPMENT (continued)

|       | DS-41 Disk Subsystem                                          | 5-3  |

|-------|---------------------------------------------------------------|------|

|       | DS-41 Disk Subsystem Standard Configurations                  | 5-4  |

|       | DS-41A Disk Subsystem Field-upgradable Configurations         | 5-4  |

|       | DS-41D Disk Daisy Chain Configurations                        | 5-4  |

|       | DS-41R Disk Subsystem Redundant Configurations                | 5-5  |

|       | DD-49 Disk Storage Unit                                       | 5-5  |

|       | Network Interfaces                                            | 5-6  |

|       | FEI-1 Front-end Interface                                     | 5-6  |

|       | Fiber-optic Link                                              | 5-6  |

|       | FEI-3 Front-end Interface                                     | 5-7  |

|       | Direct Network Connections                                    | 5-7  |

|       | High-speed External (HSX) Communications Channel              | 5-7  |

|       | High Performance Parallel Interface (HiPPI)                   | 5-7  |

|       | DEC VAX Supercomputer Gateway                                 | 5-8  |

|       | DS-40 and DS-40D Disk Subsystems Specification Sheet          | 5-9  |

|       | DS-41, DS-41D, and DS-41R Disk Subsystems Specification Sheet | 5-11 |

|       | DD-49 Disk Drive Specification Sheet                          | 5-13 |

|       | Front-end Interface Specification Sheet                       | 5-15 |

|       | FOL-3 Fiber-optic Link Specification Sheet                    | 5-17 |

|       |                                                               |      |

| 6 - S | OFTWARE OVERVIEW                                              | 6-1  |

|       | Operating Systems                                             | 6-1  |

|       | Multiprocessing                                               | 6-2  |

|       | Fortran Compilers                                             | 6-3  |

|       | C Compiler                                                    | 6-4  |

|       | Pascal                                                        | 6-4  |

|       | Cray Assembler                                                | 6-5  |

|       | Subroutine Libraries                                          | 6-5  |

|       | Utilities                                                     | 6-5  |

|       | I/O Subsystem Software                                        | 6-6  |

|       | Communications Software                                       | 6-6  |

|       | Applications                                                  | 6-7  |

|       | Software Publications                                         | 6-7  |

|       | Software Training                                             | 6-10 |

|       |                                                               |      |

| GLC   | DSSARY                                                        | GL-1 |

|       |                                                               |      |

| IND   | EX Inc                                                        | ex-1 |

# CONTENTS

| 1 - CRAY Y-MP COMPUTER SYSTEM OVERVIEW | 1-1 |

|----------------------------------------|-----|

| CRAY Y-MP Mainframe                    | 1-3 |

| I/O Subsystem                          | 1-3 |

| SSD Solid-state Storage Device         | 1-4 |

| Disk Storage Units                     | 1-5 |

| Network Interfaces                     | 1-5 |

| Operator and Maintenance Workstations  | 1-6 |

| Power and Cooling Support Equipment    | 1-6 |

|                                        |     |

### **FIGURES**

| Figure 1-1. CRAY Y-MP8 Computer System             | 1-2 |

|----------------------------------------------------|-----|

| Figure 1-2. I/O Subsystem Chassis                  | 1-3 |

| Figure 1-3. SSD Solid-state Storage Device Chassis | 1-4 |

| Figure 1-4. Typical Front-end Interface Cabinet    | 1-5 |

| Figure 1-5. CRAY Y-MP Mainframe Cooling System     | 1-7 |

| Figure 1-6. Refrigeration Condensing Unit          | 1-8 |

| Figure 1-7. Motor-generator Cabinet                | 1-9 |

| Figure 1-8. IOS and SSD Power Distribution Unit    | 1-9 |

|                                                    |     |

## **1 - CRAY Y-MP COMPUTER SYSTEM OVERVIEW**

The CRAY Y-MP computer system is a powerful, general-purpose supercomputer. The large memory and fast clock speed of the CRAY Y-MP computer system allow for faster throughput, allowing for more efficient use of computing power. The CRAY Y-MP computer system is able to achieve extremely high multiprocessing rates by efficiently using the scalar and vector processing capabilities of the multiple Central Processing Units (CPUs), combined with the systems' solid-state, random access memory (RAM), and shared registers.

The CRAY Y-MP series consists of three models: CRAY Y-MP8, CRAY Y-MP4, and CRAY Y-MP2 computer systems. The official naming convention for the CRAY Y-MP series is CRAY Y-MPn/xy, where n, x, and y represent the following numbers:

- n = maximum number of CPUs the mainframe can house

- x = number of processors in a particular configuration

- y = number of Mwords of central memory in a particular configuration

The chassis are not field upgradable beyond their maximum CPU configuration. For specific information concerning CPU and memory configurations, refer to the specification sheets at the end of Section 2.

The CRAY Y-MP computer system is carefully balanced to deliver optimum overall performance. The unique architecture of CRAY Y-MP computer systems allows faster and more efficient use of the vector and scalar processing capabilities inherent in all Cray computer systems.

Vector processing uses a single instruction to perform multiple operations on sets of ordered data. Scalar processing is a sequential operation where one instruction produces one result. When two or more vector operations are chained together, two or more operations execute simultaneously. Therefore, the computational rate for vector processing greatly exceeds that of conventional scalar processing. Scalar operations complement the vector capability by providing solutions to problems not readily adaptable to vector techniques.

The start-up time for vector operations on the CRAY Y-MP computer system is short enough so that vector processing is more efficient than scalar processing for vectors containing as few as two elements. This feature allows for fast long and short vector processing to be balanced with high-speed scalar processing, while both are supported by powerful input/output capabilities.

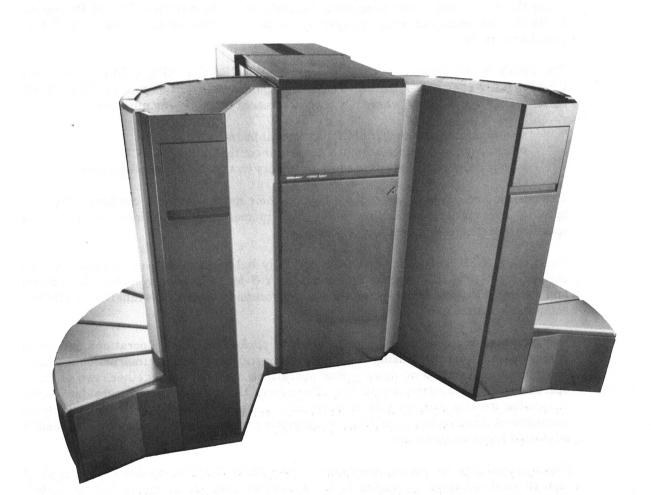

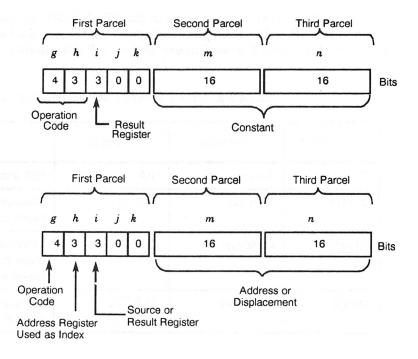

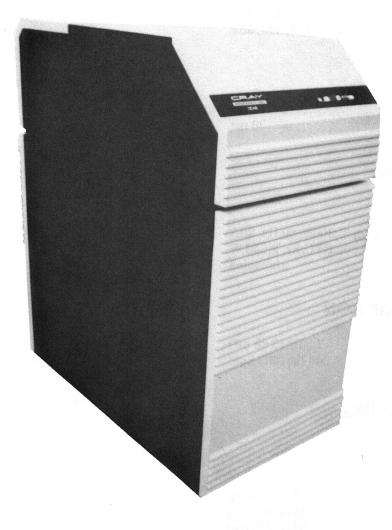

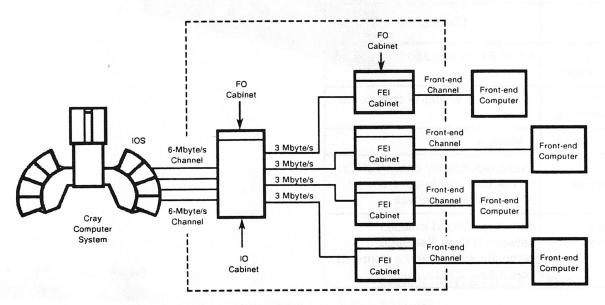

Multiple-processor CRAY Y-MP computer systems allow the use of multiprocessing or multitasking techniques. Multiprocessing allows several programs to be run concurrently on multiple CPUs of a single mainframe. Multitasking allows two or more parts of a program to run in parallel, sharing a common memory space. The CRAY Y-MP computer system consists of a mainframe, one or two I/O Subsystems (IOSs), and an optional SSD Solid-state Storage Device (SSD). Figure 1-1 shows a typical CRAY Y-MP computer system. Mass storage devices (such as disk and tape drives) and front-end interfaces (FEIs) can also be configured with the system.

Support equipment for the mainframe includes a Heat Exchanger Unit (HEU) and Refrigeration Condensing Unit (RCU) for cooling. The Power Distribution Unit (PDU) for the mainframe is located inside the mainframe; 400-Hz power is supplied by the mainframe's Motor-generator Set (MGS). Support equipment for the IOS and SSD include RCUs, PDUs, and an MGS. The following subsections introduce the system components; later sections provide more detailed information on the IOS, SSD, FEIs, and mass storage devices.

Figure 1-1. CRAY Y-MP Computer System

## **CRAY Y-MP MAINFRAME**

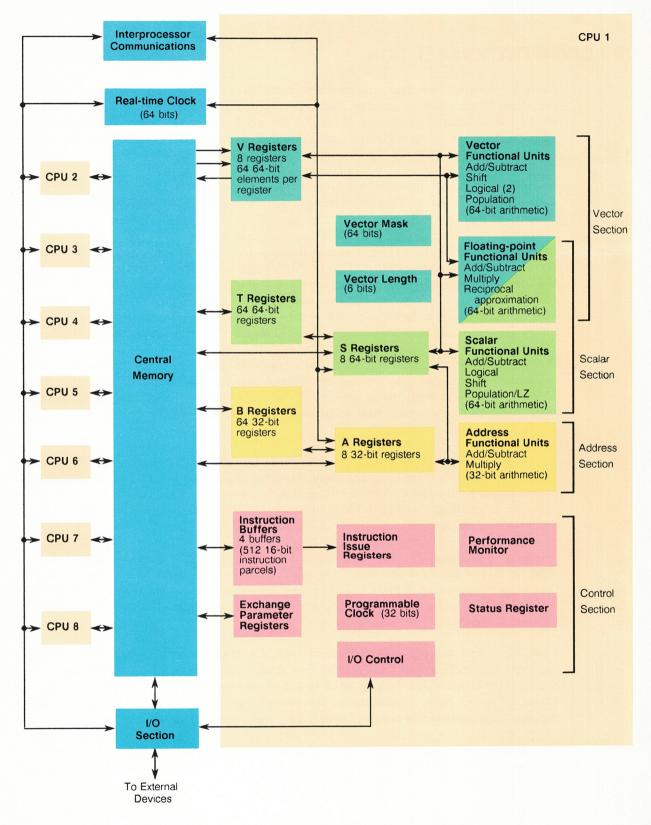

The CRAY Y-MP mainframe contains the Central Processing Units (CPUs), an I/O section, an Interprocessor Communication section, a Real-time Clock (RTC), and Central Memory. The I/O section, Interprocessor Communication section, Real-time Clock, and Central Memory are shared by all CPUs in multiprocessor computer systems.

Each CPU has a computation section, consisting of operating registers and functional units, and a control section. The control section determines instruction issue and coordinates the three types of processing (vector, scalar, or address).

Refer to Section 2 for more specific information on the CRAY Y-MP mainframes.

### **I/O SUBSYSTEM**

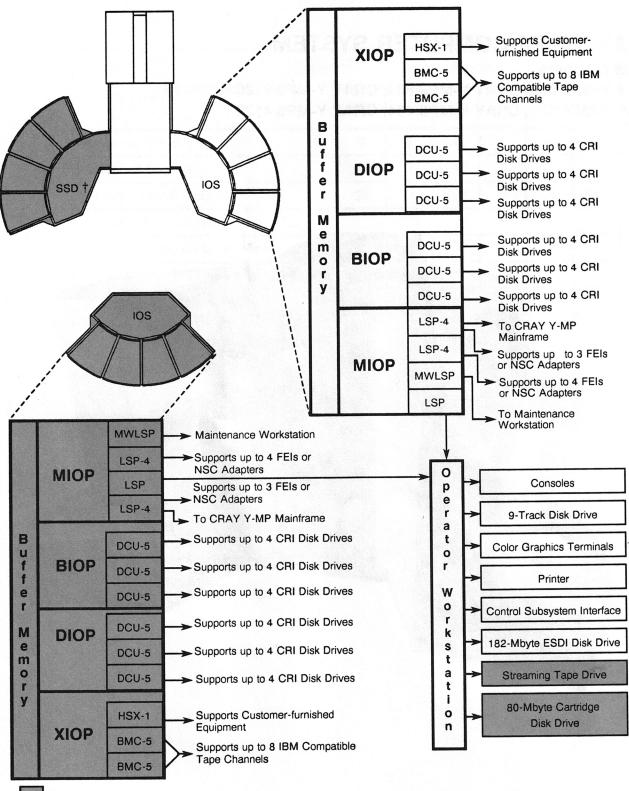

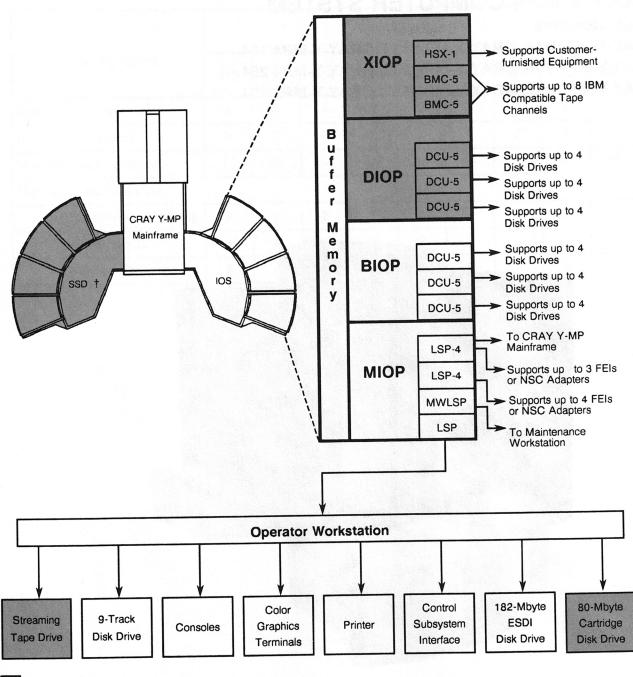

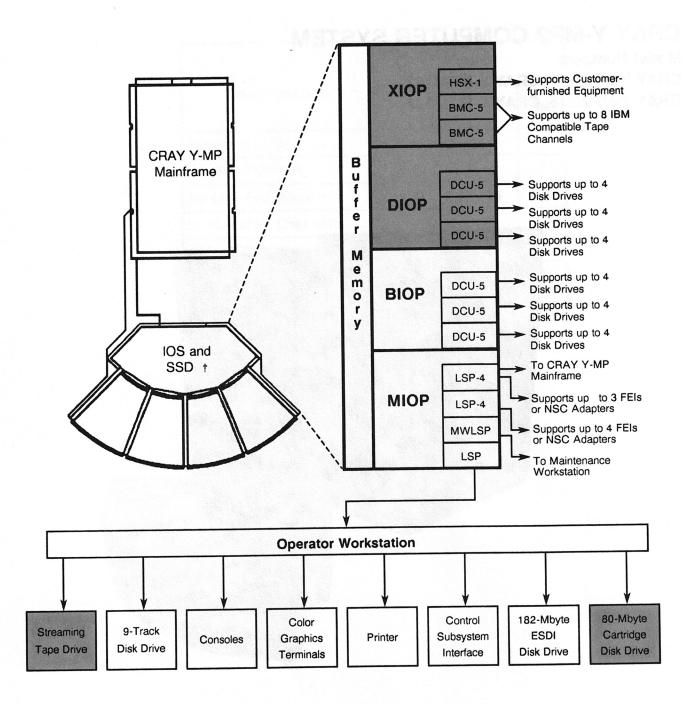

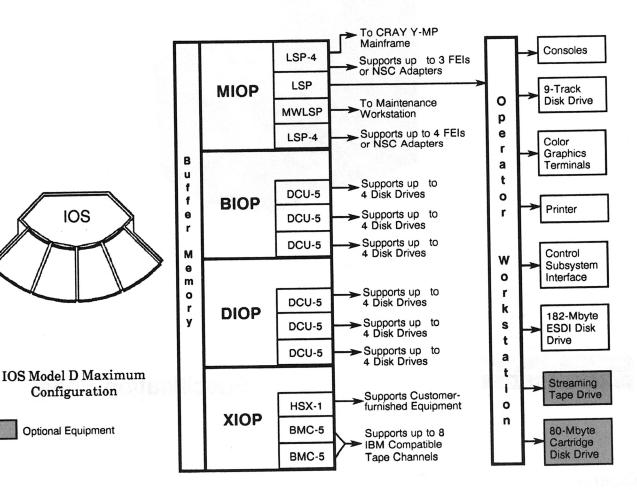

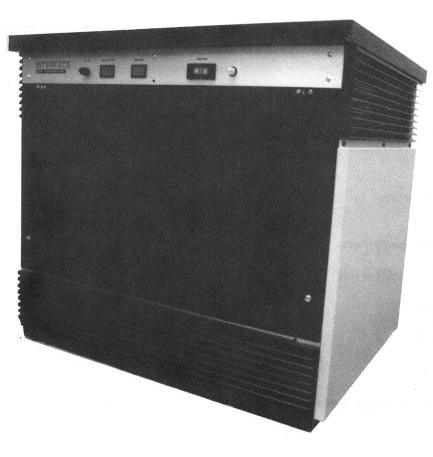

The CRAY Y-MP computer system includes an I/O Subsystem (IOS); a second IOS is optional with the CRAY Y-MP8 computer system. Each IOS (a single IOS chassis, referred to as the IOC, is shown in Figure 1-2) has multiple I/O Processors (IOPs), a Buffer Memory, and required interfaces. It is designed for fast data transfer between front-end computers, peripheral devices, storage devices, and the IOS's Buffer Memory, or between its Buffer Memory and the Central Memory of the CRAY Y-MP mainframe.

Figure 1-2. I/O Subsystem Chassis

The IOS is configured with a variety of different IOPs; each IOP controls different portions of the system. The number of IOPs configured with a system is site dependent. Each IOP has a memory section, a control section, a computation section, and an I/O section. I/O sections are independent and handle some portion of the I/O requirements for the IOS. IOS hardware allows simultaneous data transfers between the IOPs and the mainframe's Central Memory over 100-Mbyte/s I/O channels.

The IOS also interfaces with the High-speed External communications (HSX) channel. The HSX channel connects external peripheral equipment, such as high-speed graphic devices, to the CRAY Y-MP mainframe. Cray Research, Inc. (CRI) does not provide the external peripheral equipment, but provides the hardware connections and software drivers for the channel.

The HSX channel can also be configured through the SSD. With this configuration data moves between Central Memory and the SSD over the conventional SSD channel, and then transfers to the IOS/HSX channel.

Refer to Section 3 of this manual for more information on the IOS.

## SSD SOLID-STATE STORAGE DEVICE

The SSD is an optional high-performance device used for temporary data storage. Figure 1-3 shows a stand-alone SSD chassis. The SSD transfers data between the mainframe's Central Memory and the SSD through special 1,000-Mbyte/s channels. The actual speed of these transfers depends on the SSD and CRAY Y-MP system configuration. The SSD can also be connected directly to an IOP over a 100-Mbyte/s channel pair. The SSD-3I and SSD-5I are special versions of the SSD that are housed within the IOC.

Refer to Section 4 of this manual for specific information on the SSD.

Figure 1-3. SSD Solid-state Storage Device Chassis

## **DISK STORAGE UNITS**

For mass storage, the CRAY Y-MP computer system uses CRI Disk Storage Units (DSUs). A Disk Controller Unit (DCU) interfaces the DSUs to an IOP within the IOS. The IOP and the DCU can transfer data between the IOP and multiple DSUs without missing data or skipping revolutions even when all DSUs are operating at full speed. Refer to "Disk Controller Units and Disk Storage Units" in Section 5 of this manual for more information.

### NETWORK INTERFACES

The CRAY Y-MP mainframe is designed to communicate easily with front-end computer systems and computer networks.

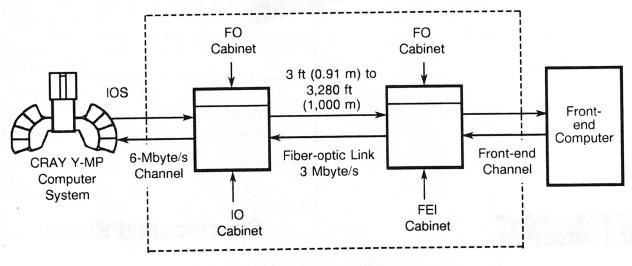

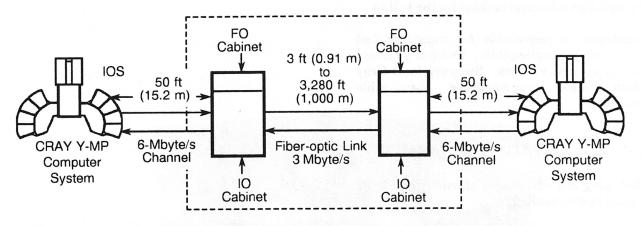

Standard front-end interfaces (FEIs) connect either the I/O channels of the CRAY Y-MP mainframe or IOS to channels of front-end computers. This connection provides input data to the CRAY Y-MP computer system and receives output from it for distribution to peripheral equipment. An FEI compensates for differences in channel widths, machine word size, electrical logic levels, and control signals.

Some FEI's are housed in a stand-alone cabinet located near the host computer (refer to Figure 1-4), while some install directly into the front-end computer system. In either case, operation of the FEI is invisible to both the front-end and Cray user.

As an option, a fiber-optic link is available for some FEIs to provide front-end connections of up to 3,280 ft (1,000 m) and complete electrical separation from the CRAY Y-MP computer system.

The CRAY Y-MP mainframe can be connected to computer networks directly, or through a front-end computer system. Refer to "Network Interfaces" in Section 5 of this manual for specific information.

Figure 1-4. Typical Front-end Interface Cabinet

## **OPERATOR AND MAINTENANCE WORKSTATIONS**

VMEbus technology is used to provide two workstations on the CRAY Y-MP computer system: the system Operator Workstation (OWS) and the Maintenance Workstation (MWS). Both workstations run UNIX System V software. The OWS is a microcomputer system that performs the following functions:

- System operator interface

- System deadstart and master clear functions

- Software maintenance utilities

- Local tape and local printer control

- System time-of-day clock

In addition, the OWS provides enhanced features, such as a Control Subsystem Network interface, which can be used to network workstations in a multiple system site or for multiple system operators.

The OWS communicates with the CRAY Y-MP computer system through a 6-Mbyte/s I/O channel from an IOP in the IOS. The tape drives, disks, printer, and time-of-day clock are available to the mainframe over this 6-Mbyte/s channel.

The MWS is a microcomputer system used for hardware maintenance and monitoring. The MWS is owned by Cray Research, Inc. and is supplied as part of the maintenance contract and therefore is not part of the customer's system. The MWS is not connected to the customer's network.

## POWER AND COOLING SUPPORT EQUIPMENT

CRAY Y-MP computer systems require support equipment for power and cooling. Power is supplied by MGSs and PDUs. The system cooling components include a Heat Exchanger Unit (HEU) and RCUs. The remainder of this section defines and explains the various mainframe, IOS, and SSD support equipment. Refer to the appropriate Site Engineering manuals listed in the Preface for more information on power and cooling requirements.

The CRAY Y-MP mainframe power supplies and voltage-adjusting controls are located in the mainframe chassis; a separate PDU is not needed for the mainframe. The 400-Hz power from the MGSs is distributed among the power supplies (MGSs are described later in this section).

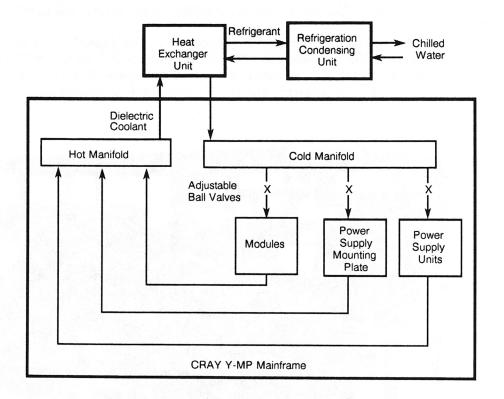

The CRAY Y-MP mainframe is cooled by an HEU and an RCU. The HEU contains a pump that circulates chilled dielectric coolant (such as Fluorinert liquid) through each module, power supply, and the power supply mounting plate (refer to Figure 1-5). Each circulation loop has an adjustable ball valve that controls the flow rate. The temperature of the modules and power supplies is changed by increasing or decreasing the flow rate.

**Note**: Fluorinert liquid is a safe product when used properly. When exposed to an excessive heat source, Fluorinert liquid can decompose and produce hazardous by-products. The *Safe Use and Handling of Fluorinert Liquids* Manual (publication number HR-0306) provides specific guidelines and information regarding Fluorinert liquid.

The mainframe RCU cools the dielectric coolant in the HEU with a refrigerant. The RCU itself is cooled by customer-supplied chilled water; the RCU is described later in this section.

Figure 1-5. CRAY Y-MP Mainframe Cooling System

Because of the intense heat created by the density of the circuitry, the CRAY Y-MP mainframe has a monitoring system consisting of PC boards and a system control panel. This panel is located at the power supply end of the mainframe chassis. The panel contains indicators that allow the following functions to be monitored:

- DC voltages provides voltage level monitoring, loss of voltage protection, and over-voltage protection.

- AC voltages monitors MGS phase-to-phase and phase-to-neutral voltages.

- Temperatures monitors power supply mounting plate and coolant temperatures to protect the mainframe from overheating.

- Pressure provides protection against high or low coolant pressure in the cooling system.

- Coolant flow monitors module plate flow rates to protect the mainframe from overheating.

The monitoring system provides a method for the system attendant to observe these conditions. The monitoring system also functions as a backup system that can automatically shut down the mainframe if an abnormal condition exists and the system attendant fails to notice the condition. In addition to these automatic monitoring features, the AC output voltage on the MGSs can be set from this panel.

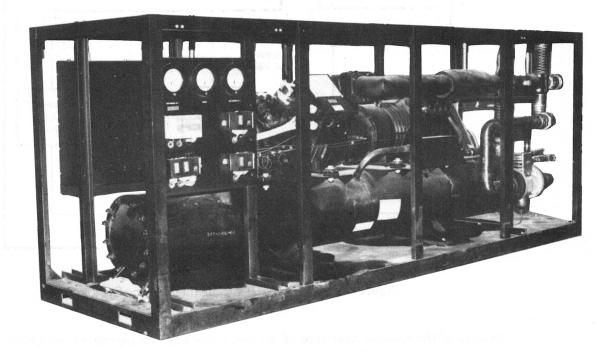

An RCU contains the major components of the refrigeration system used to cool the mainframe, the IOS, and the SSD. Heat is removed from the RCU by a second-level cooling system that is not part of the computer system. The number of RCUs needed is system- and site-dependent. Figure 1-6 shows the RCU without the covers.

Figure 1-6. Refrigeration Condensing Unit

The CRAY Y-MP computer system contains up to three MGSs. The maximum configuration includes one MGS for the mainframe, one MGS for the IOS and SSD, and a standby. Each MGS converts primary power from commercial power mains to the 400-Hz power used by the mainframe, the IOS, and the SSD. The MGS also isolates these components from transients and fluctuations on the commercial power mains. An MGS cabinet is shown in Figure 1-7.

Figure 1-7. Motor-generator Cabinet

The IOS and SSD each have independent PDUs. The PDU contains temperature and voltage-monitoring equipment that checks temperatures at strategic locations on the IOS and SSD chassis (the automatic warning system alerts the system attendant if overheating or excessive cooling occurs). If the system attendant fails to notice these conditions, the PDU powers down the equipment. Figure 1-8 shows the PDU used by the IOS and SSD.

Figure 1-8. IOS and SSD Power Distribution Unit

# CONTENTS

| <b>2 - C</b> | RAY Y-MP MAINFRAME                                | 2-1  |

|--------------|---------------------------------------------------|------|

|              | CPU Shared Resources                              | 2-1  |

|              | Central Memory                                    | 2-1  |

|              | I/O Section                                       | 2-2  |

|              | Interprocessor Communication Section              | 2-2  |

|              | Real-time Clock                                   | 2-2  |

|              | CPU Computation Section                           | 2-3  |

|              | Registers                                         | 2-5  |

|              | Address Registers                                 | 2-5  |

|              | Scalar Registers                                  | 2-6  |

|              | Vector Registers                                  | 2-6  |

|              | Functional Units                                  | 2-7  |

|              | Address Functional Units                          | 2-7  |

|              | Scalar Functional Units                           | 2-7  |

|              | Vector Functional Units                           | 2-8  |

|              | Floating-point Functional Units                   | 2-9  |

|              | Functional Unit Operations                        | 2-10 |

|              | Logical Operations                                | 2-10 |

|              | Integer Arithmetic                                | 2-11 |

|              | Floating-point Arithmetic                         | 2-12 |

|              | CPU Control Section                               | 2-22 |

|              | Exchange Mechanism                                | 2-22 |

|              | Exchange Sequence                                 | 2-22 |

|              | Exchange Package                                  | 2-22 |

|              | Instruction Fetch                                 | 2-27 |

|              | Instruction Issue                                 | 2-27 |

|              | Programmable Clock                                | 2-28 |

|              | Performance Monitor                               | 2-28 |

|              | Status Register                                   | 2-28 |

|              | Special Features of the CRAY Y-MP Computer System | 2-29 |

|              | Pipelining and Segmentation                       | 2-29 |

|              | Functional Unit Independence                      | 2-29 |

|              | Vector Processing                                 | 2-30 |

|              | Definition of Vector Processing                   | 2-30 |

|              | Advantages of Vector Processing                   | 2-31 |

|              | Vector Chaining                                   | 2-31 |

|              | Types of Vector Instructions                      | 2-32 |

| CPU Instructions                                                                               | 2-37 |

|------------------------------------------------------------------------------------------------|------|

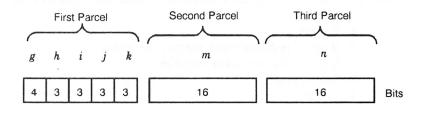

| Instruction Formats                                                                            | 2-37 |

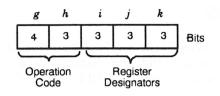

| 1-parcel Instruction Format with Discrete <i>j</i> and <i>k</i> Fields                         | 2-37 |

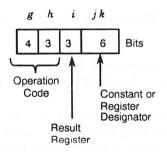

| 1-parcel Instruction Format with Combined <i>j</i> and <i>k</i> Fields                         | 2-38 |

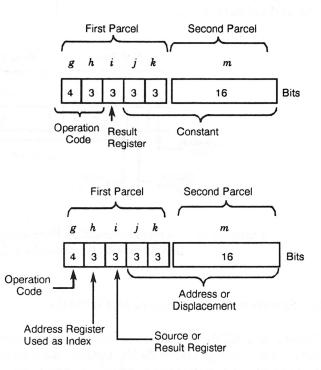

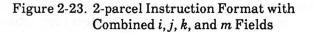

| 2-parcel Instruction Format with Combined <i>j</i> , <i>k</i> , and <i>m</i> Fields            | 2-38 |

| 2-parcel Instruction Format with Combined <i>i</i> , <i>j</i> , <i>k</i> , and <i>m</i> Fields | 2-39 |

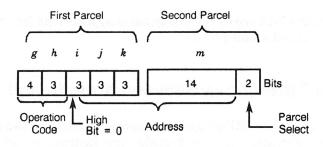

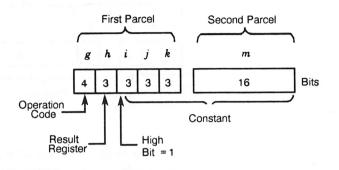

| 3-parcel Instruction Format with Combined <i>m</i> and <i>n</i> Fields                         | 2-40 |

| Instruction Differences Between X-Mode and Y-Mode                                              | 2-40 |

| Special Register Values                                                                        | 2-42 |

| Monitor Mode Instructions                                                                      | 2-43 |

| Special CAL Syntax Forms                                                                       | 2-43 |

| CPU Instruction Summary                                                                        | 2-43 |

| Functional Units Instruction Summary                                                           | 2-44 |

| Functional Instruction Summary                                                                 | 2-45 |

| CRAY Y-MP8 Computer System Specification Sheet                                                 | 2-67 |

| CRAY Y-MP4 Computer System Specification Sheet                                                 | 2-71 |

| CRAY Y-MP2 Computer System Specification Sheet                                                 | 2-75 |

## FIGURES

| Figure 2-1. 8-processor CRAY Y-MP Computer System Block Diagram                                             | 2-4  |

|-------------------------------------------------------------------------------------------------------------|------|

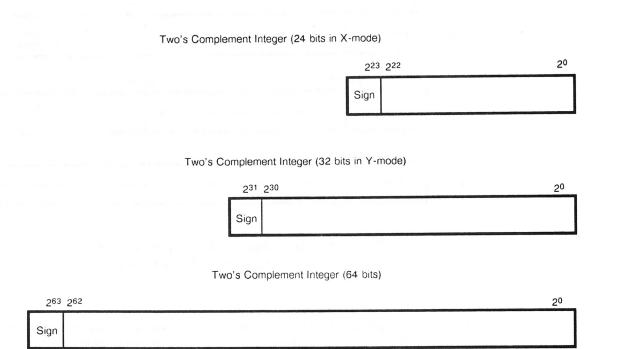

| Figure 2-2. Integer Data Formats                                                                            | 2-11 |

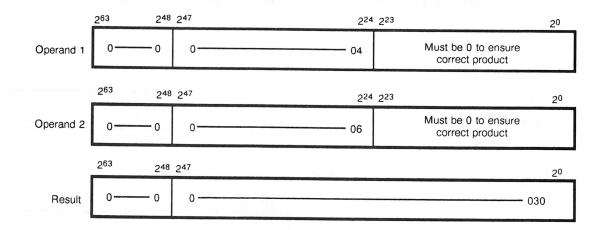

| Figure 2-3. 24-bit Integer Multiply Performed in Floating-point Multiply Functional Unit                    | 2-12 |

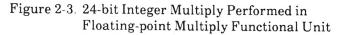

| Figure 2-4. 32-bit Integer Multiply Performed in Floating-point Multiply Functional Unit                    | 2-13 |

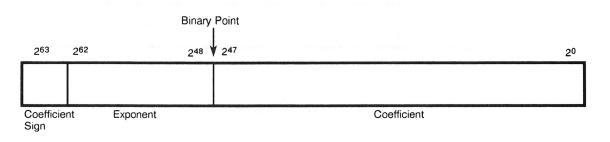

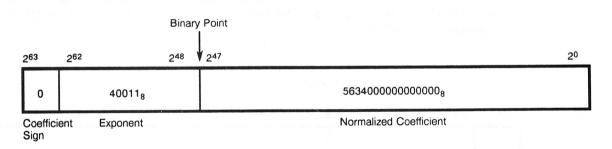

| Figure 2-5 Floating-point Data Format                                                                       | 2-13 |

| Figure 2-6 Internal Representation of Floating-point Number                                                 | 2-14 |

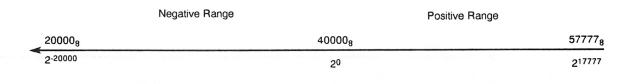

| Figure 2-7 Biased and Unbiased Exponent Range                                                               | 2-15 |

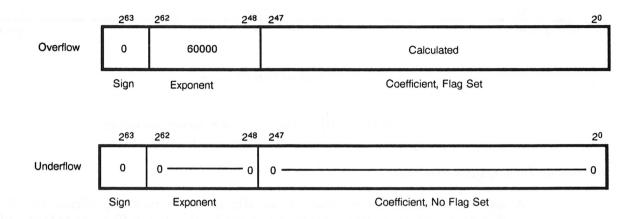

| Figure 2-8. Floating-point Add and Multiply Range Errors                                                    | 2-16 |

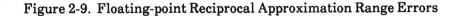

| Figure 2-9. Floating-point Reciprocal Approximation Range Errors                                            | 2-16 |

| Figure 2-10 Newton's Method of Approximation                                                                | 2-19 |

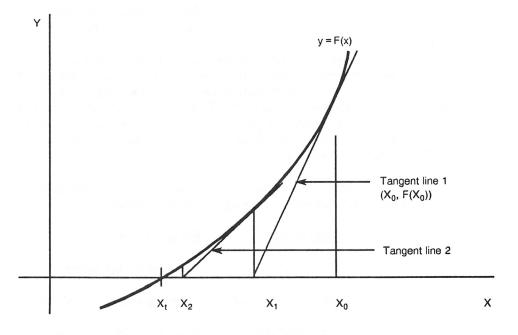

| Figure 2-11 Segmentation and Pipelining Example                                                             | 2-30 |

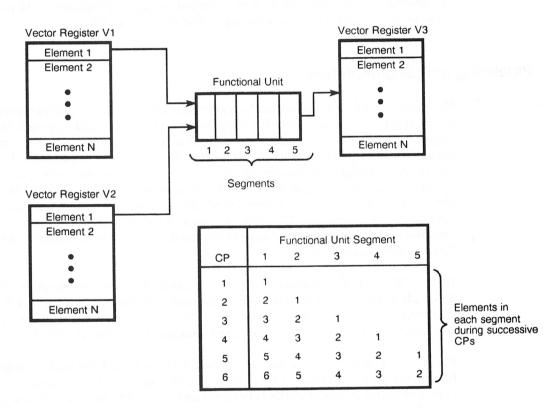

| Figure 2-12 Vector Chaining Example                                                                         | 2-32 |

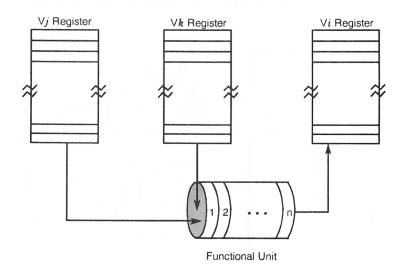

| Figure 2-13 Vector vector Operand Instructions                                                              | 2-33 |

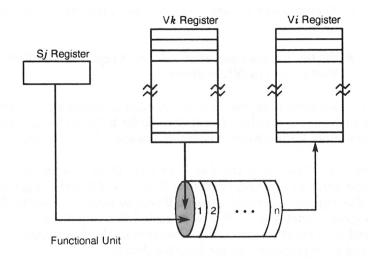

| Figure 2-14. Vector-scalar Operand Instructions                                                             | 2-34 |

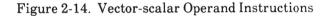

| Figure 2-15. Vector Memory Instructions                                                                     | 2-34 |

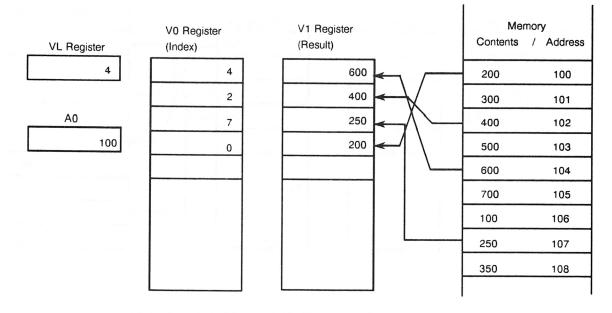

| Figure 2-16. Gather Instruction Example                                                                     | 2-35 |

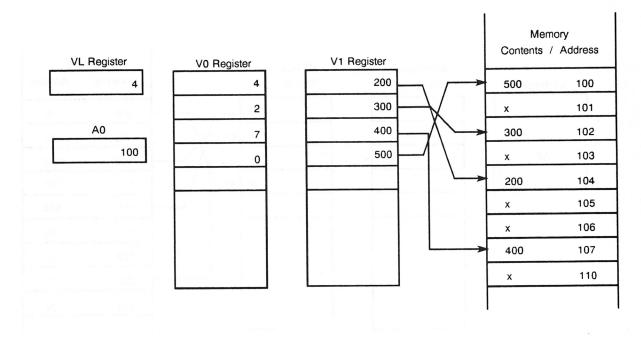

| Figure 2-17. Scatter Instruction Example                                                                    | 2-36 |

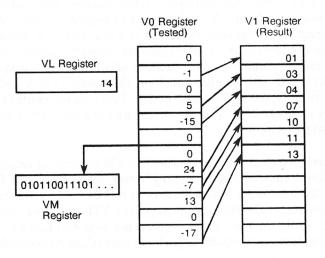

| Figure 2-18. Compressed Index Example                                                                       | 2-36 |

| Figure 2-19. General Format for Instructions                                                                | 2-37 |

| Figure 2-20. 1-parcel Instruction Format with Discrete j and k Fields                                       | 2-38 |

| Figure 2-21. 1-parcel Instruction Format with Combined j and k Fields                                       | 2-38 |

| Figure 2-22. 2-parcel Instruction Format with Combined <i>j</i> , <i>k</i> , and <i>m</i> Fields            | 2-39 |

| Figure 2-23. 2-parcel Instruction Format with Combined <i>i</i> , <i>j</i> , <i>k</i> , and <i>m</i> Fields | 2-39 |

## FIGURES (continued)

| 'igure 2-24. 2-parcel Instruction Format for a 24-bit Immediate Constant with      |      |

|------------------------------------------------------------------------------------|------|

| Combined <i>i</i> , <i>j</i> , <i>k</i> , and <i>m</i> Fields                      | 2-40 |

| igure 2-25. 3-parcel Instruction Format with Combined <i>m</i> and <i>n</i> Fields | 2-41 |

## TABLES

| Table 2-1. CRAY Y-MP 3-parcel Instruction         | 2-41 |

|---------------------------------------------------|------|

| Table 2-2. CRAY Y-MP/X-MP Instruction Differences | 2-42 |

| Table 2-3. Special Register Values                | 2-42 |

## 2 - CRAY Y-MP MAINFRAME

This section describes the major functional areas of a CRAY Y-MP mainframe, special features of the mainframe, and a summary of the Cray Assembly Language (CAL) instruction set. For specific information concerning the CRAY Y-MP8, CRAY Y-MP4, and CRAY Y-MP2 systems, refer to the specification sheets at the end of this section.

## **CPU SHARED RESOURCES**

The Central Processing Units (CPUs) of the CRAY Y-MP computer system share several functional areas (or sections) of the mainframe. These sections include Central Memory, the I/O section, the Interprocessor communication section, and the Real-time Clock. The following subsections describe these functional areas.

### Central Memory

The CRAY Y-MP Central Memory is shared by the CPUs and the I/O section. Central Memory is divided into interleaved banks. This arrangement improves memory access speed by allowing simultaneous and overlapping memory references. Simultaneous references are two or more references that begin at the same time. Overlapping references are one or more references that begin while another reference is in progress. Refer to the specification sheets at the end of this section for more information on memory size and number of banks for each model.

Each CPU in the system has four parallel memory ports. Each port performs specific functions, allowing different types of memory transfers to occur simultaneously. To further enhance memory operations, the bidirectional memory mode allows block read and writes to occur concurrently.

The CRAY Y-MP computer system has built-in resolution hardware to minimize the delays caused by memory conflicts and to maintain the integrity of all memory references when conflicts occur. A memory conflict occurs when more than one reference is made to the same area of Central Memory.

To protect data, single-error correction/double-error detection (SECDED) logic is used in Central Memory and on data channels to or from Central Memory. When data is written into Central Memory, a checkbyte (an 8-bit Hamming<sup>†</sup> code) is generated for the word and stored with that word. When the word is read from Central Memory, the checkbyte and data word are processed to determine if any bits were altered. If no errors occurred, the word is passed without modification.

<sup>&</sup>lt;sup>†</sup> Hamming, R. W. "Error Detection and Correcting Codes." Bell System Technical Journal. 29.2 (1950): 147-160.

If an error occurred, the 8 bits of the checkbyte are analyzed by the logic to find the number of altered bits. If only a single bit was altered, the correction logic resets that bit to the correct state and passes the corrected word on. The Memory Error flag in the Exchange Package sets to indicate that an error occurred, which can generate an interrupt. (Refer to "Flag Register Field" in this section for more information on the Memory Error flag.) Error information is also sent to an Error logger.

If more than a single bit is altered, the logic cannot correct the word and the results are unpredictable. When a double error is detected, the Memory Error flag in the Exchange Package sets to indicate an error occurred, which can generate an interrupt. Error information is also sent to an Error logger.

### I/O Section

The I/O section is shared by all CPUs in multiprocessor computer systems. The mainframe supports three channel types identified by their maximum transfer rates: 6 Mbyte/s, 100 Mbyte/s, and 1000 Mbyte/s. The 6-Mbyte/s channels are used to transfer control information between the mainframe and a Cray I/O Subsystem (IOS). The 100-Mbyte/s channels are used to transmit data between the mainframe and an IOS. The 1000-Mbyte/s channels transfer data between the mainframe and an SSD solid-state storage device (SSD). The IOS and SSD are high-speed data transfer devices designed to support CRAY Y-MP mainframe processing. Refer to the specification sheets at the end of this section for more information on channel configurations for the different models.

### Interprocessor Communication Section

The interprocessor communication section of the mainframe contains clusters of shared registers for interprocessor communication and synchronization. Each cluster consists of Shared Address (SB), Shared Scalar (ST), and Semaphore (SM) registers.

The SB and ST registers pass address and scalar information from one CPU to another, while the SM registers control activity between CPUs.

Each CPU Cluster Number (CLN) register determines which set of shared registers is accessed by a CPU (clustering). The cluster may be accessed by any CPU to which it is allocated in either user or system (monitor) mode. Any CPU in monitor mode can interrupt any other CPU and cause it to switch from user to monitor mode. Additionally, each CPU in a cluster can asynchronously perform scalar or vector operations dictated by user programs. The hardware also provides built-in detection of system deadlock within the cluster; a deadlock condition occurs when all CPU's in a cluster are holding issue on a Test and Set instruction.

### **Real-time Clock**

The CRAY Y-MP mainframe contains one Real-time Clock (RTC) that is shared by all the CPUs. This clock consists of a 64-bit counter that advances one count each clock period (CP). Because the clock advances synchronously with program execution, it can be

used to time the program to an exact number of CPs. Contents of the RTC register can be read into or loaded from a Scalar (S) register.

## **CPU COMPUTATION SECTION**